#### PAPER

## First demonstration of robust tri-gate $\beta$ -Ga<sub>2</sub>O<sub>3</sub> nano-membrane field-effect transistors

To cite this article: Hagyoul Bae et al 2022 Nanotechnology 33 125201

View the article online for updates and enhancements.

#### You may also like

- <u>Progress in state-of-the-art technologies of</u> <u>Ga\_O\_3 devices</u> Chenlu Wang, Jincheng Zhang, Shengrui Xu et al.

- Influence of N<sub>2</sub>O/TEGa Ratio on Deposition of -Ga<sub>2</sub>O<sub>3</sub> Films and Performance of Au--Ga<sub>2</sub>O<sub>3</sub>-Au Solar-Blind Photodetectors Chun-Ying Huang, Yen-Yang Liu, Pei-Te Lin et al.

- <u>-Ga<sub>2</sub>O<sub>3</sub> for wide-bandgap electronics and</u> optoelectronics Zbigniew Galazka

## IOP ebooks<sup>™</sup>

Bringing together innovative digital publishing with leading authors from the global scientific community.

Start exploring the collection-download the first chapter of every title for free.

Nanotechnology 33 (2022) 125201 (6pp)

# First demonstration of robust tri-gate $\beta$ -Ga<sub>2</sub>O<sub>3</sub> nano-membrane field-effect transistors

### Hagyoul Bae<sup>1,2</sup>, Tae Joon Park<sup>3</sup>, Jinhyun Noh<sup>1,2</sup>, Wonil Chung<sup>1,2</sup>, Mengwei Si<sup>4</sup>, Shriram Ramanathan<sup>3</sup> and Peide D Ye<sup>1,2</sup>

<sup>1</sup>Electrical and Computer Engineering, Purdue University, West Lafayette, IN 47907, United States of America

<sup>2</sup> Birck Nanotechnology Center, Purdue University, West Lafayette, IN 47907, United States of America

<sup>3</sup> Materials Engineering, Purdue University, West Lafayette, IN 47907, United States of America

<sup>4</sup> Electronic Engineering, Shanghai Jiao Tong University, Shanghai 200240, People's Republic of China

E-mail: yep@purdue.edu

Received 4 September 2021, revised 12 November 2021 Accepted for publication 1 December 2021 Published 24 December 2021

#### Abstract

Nano-membrane tri-gate  $\beta$ -gallium oxide ( $\beta$ -Ga<sub>2</sub>O<sub>3</sub>) field-effect transistors (FETs) on SiO<sub>2</sub>/Si substrate fabricated via exfoliation have been demonstrated for the first time. By employing electron beam lithography, the minimum-sized features can be defined with the footprint channel width of 50 nm. For high-quality interface between  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> and gate dielectric, atomic layer-deposited 15 nm thick aluminum oxide (Al<sub>2</sub>O<sub>3</sub>) was utilized with tri-methyl-aluminum (TMA) self-cleaning surface treatment. The fabricated devices demonstrate extremely low subthreshold slope (*SS*) of 61 mV dec<sup>-1</sup>, high drain current ( $I_{DS}$ ) ON/OFF ratio of 1.5 × 10<sup>9</sup>, and negligible transfer characteristic hysteresis. We also experimentally demonstrated robustness of these devices with current–voltage (I–V) characteristics measured at temperatures up to 400 °C.

Keywords: tri-gate,  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FETs, exfoliation, wide bandgap, atomic layer deposition, single-channel, multi-channel

(Some figures may appear in colour only in the online journal)

#### 1. Introduction

$\beta$ -Ga<sub>2</sub>O<sub>3</sub> is one of the promising materials for next-generation power electronics owing to its ultra-wide bandgap of 4.6–4.9 eV, high breakdown electric field of 8 MV cm<sup>-1</sup>, high electron mobility of 100–150 cm<sup>2</sup> V<sup>-1</sup>·s<sup>-1</sup>, and sustainability for hightemperature operation and mass production with low-cost fabrication [1–8]. In addition, the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> material has a higher Baliga's figure-of-merit (FOM) than that of silicon carbide (SiC) and gallium nitride (GaN) [9, 10]. Owing to these advantages, monolithic  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> transistors could also be considered for high-temperature operation in harsh environments. In particular, stable operation of electronic devices in severe conditions, mainly at high temperatures, is indispensable for many applications in the defense, automotive, nuclear instrumentation, and aerospace fields [11, 12]. Recently, several studies have demonstrated improved electrical performances of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FETs by using double-gate [13], multi-channel with wrap-gate [14], vertical channel [15], back-gate [16], and recessed-gate [17, 18] devices. In particular, among these advanced technologies, structure innovation to enhance gate controllability to boost higher current density and suppress interface or short-channel effect becomes critical during device research [19, 20]. There are still opportunities to achieve better switching characteristics, higher integration density, and lower power consumption in  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> materials and device development.

In this study, the fabrication and performance of tri-gate  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FETs with single and multi channel structures formed from nano-membranes are presented. In the single channel structure, a narrow channel with a width ( $W_{ch}$ ) of 50 nm is fabricated to exploit the high ON/OFF ratio of  $I_{DS}$

1

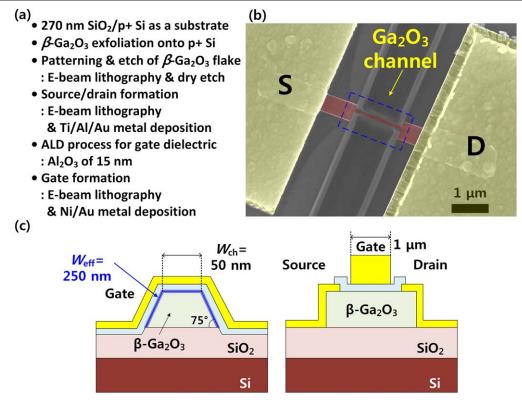

**Figure 1.** (a) Process flow for device fabrication of exfoliated tri-gate  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> nano-membrane FETs with the top-gate structure. (b) SEM image of a fabricated device. (c) Cross-sectional schematics along both channel width and length directions.

and superior subthreshold slope, while maintaining reliable performance at temperature from room temperature (RT) to 400 °C.

#### 2. Device fabrication

Figure 1(a) lists the key fabrication steps for the tri-gate nanomembrane  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FETs on the SiO<sub>2</sub>/Si substrate. For the fabrication of the top-gate devices, thin (100)  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> nanomembranes with a Sn doping concentration of 2.7  $\times$  $10^{18}$  cm<sup>-3</sup> was transferred from the bulk  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> substrate onto a p + Si wafer with a 270 nm  $SiO_2$  as gate dielectric. The tri-gate active channel region was defined by electron (e)beam lithography and the dry-etch process. To form narrower  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> with tri-gate structure, we used a BCl<sub>3</sub>/Ar gas mixture in an inductively coupled plasma-reactive ion etching (ICP-RIE) system (Panasonic E620 Etcher) for 15 min [21]. The etching rate of (100)  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> is about 10 nm min<sup>-1</sup> under process conditions: RF power of 100 W; BCl<sub>3</sub> flow of 15 sccm; Ar flow of 60 sccm; and pressure of 0.6 Pa. Subsequently, the source (S) and drain (D) regions were formed via e-beam lithography patterning, Ti/Al/Au (15/60/50 nm) metallization, and lift-off process. No post-deposition thermal annealing was performed. By employing the atomic layer deposition (ALD) process, high-quality Al<sub>2</sub>O<sub>3</sub> gate dielectric was deposited to minimize gate leakage current and highquality interface by self-cleaning effect using TMA as the precursor [22, 23]. Subsequently, e-beam lithography was carried out for gate patterning and Ni/Au (50/80 nm) metal gate was deposited via an e-beam evaporator. Figure 1(b) presents the scanning electron microscope (SEM) image showing the etched  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> channel with  $W_{ch}$  of 50 nm, a gate length ( $L_G$ ) of 1  $\mu$ m, and a channel height ( $H_{ch}$ ) of 95 nm. As the fabricated device has a 3D tri-gate structure, the total effective channel width ( $W_{eff}$ ) is approximately 250 nm, which is 5 times wider than the footprint  $W_{ch}$  of 50 nm. Figure 1(c) shows the cross-sectional view of the fabricated device along both channel width and length directions. Using atomic force microscopy (AFM), the measured physical thickness of the exfoliated  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> nano-membrane is approximately 95 nm.

#### 3. Experimental results and discussion

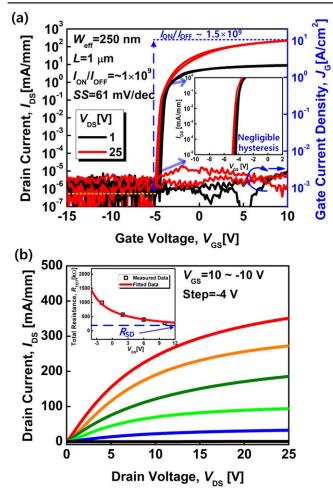

Figure 2(a) shows the measured transfer characteristics  $(I_{\rm DS}-V_{\rm GS})$  of the fabricated tri-gate  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FET with  $W_{\rm eff}$  of 250 nm and  $L_{\rm G}$  of 1  $\mu$ m, showing the following excellent electrical performances: (1)  $I_{\rm ON} = 350$  mA mm<sup>-1</sup> normalized with the  $W_{\rm eff}$ ; (2)  $I_{\rm ON}/I_{\rm OFF} = 1.5 \times 10^9$ ; (3)  $SS_{\rm min} = 61$  mV dec<sup>-1</sup>; (4) DIBL = 12 mV V<sup>-1</sup>; (5)  $V_{\rm hys} = 30$  mV. The electrical characterizations were performed using a Keysight B1500 semiconductor parameter analyzer, a Keithley 4200-SCS parameter analyzer with a high-temperature measurement system (Micromanipulator H1000 Thermal Chuck System), and a Cascade Summit probe station. Figure 2(b) shows the measured output characteristics ( $I_{\rm DS}-V_{\rm DS}$ ) as a function of  $V_{\rm GS}$  from 0 to -20 V. A maximum drain current density ( $I_{\rm DS}$ max) of 350 mA mm<sup>-1</sup> in the fabricated device on

**Figure 2.** (a) Measured  $I_{DS}-V_{GS}$  transfer characteristics and (b)  $I_{DS}-V_{DS}$  output characteristics of the fabricated tri-gate  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FET.

the  $SiO_2/Si$  substrate is obtained, which is higher than that obtained in our previous study of top-gate devices on SiO<sub>2</sub>/Si substrate [24]. In this study, improvements, i.e. steep SS and high  $I_{\rm ON}/I_{\rm OFF}$  ratio were obtained by using SiO<sub>2</sub>/Si substrate instead of diamond substrate in terms of cost effectiveness and process simplification, but we expect that the tri-gate  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FETs on diamond substrate could give rise to further improved IDS\_max due to its high thermal conductivity  $(\kappa = 1000-2200 \text{ W m}^{-1} \cdot \text{K}^{-1})$ , as a further study. This proposed tri-gate structure enables to control  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> channel from three sides of the gate and improve the gate electrostatics significantly as in Si CMOS technology. The threshold voltage  $(V_{\rm T})$  is determined to be -2.8 V by the constant current method. The parasitic source/drain resistances  $(R_{SD})$ is obtained by extrapolating  $V_{GS}$  based on channel resistance method (CRM) as shown in the inset of figure 2(b) [25]. The  $R_{\rm C}$  and sheet resistance ( $R_{\rm SH}$ ) is extracted to be 8.0  $\Omega$ ·mm and 6.2 k $\Omega/\Box$ , respectively. Further studies on  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> contacts are highly demanded in the development of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> device technology [26].

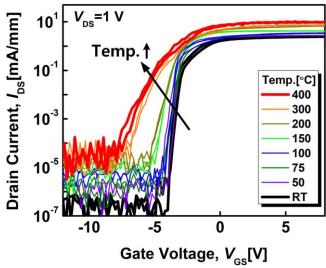

The measured  $I_{DS}-V_{GS}$  characteristics of the fabricated tri-gate  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FET on the SiO<sub>2</sub>/Si substrate measured at various temperatures ranging from RT to 400 °C are shown in figure 3 with negligible hysteresis. Although  $I_{OFF}$  starts to

**Figure 3.** Measured  $I_{\rm DS}-V_{\rm GS}$  characteristics of the fabricated tri-gate  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FETs on SiO<sub>2</sub>/Si substrate at various temperatures ranging from RT to 400 °C.

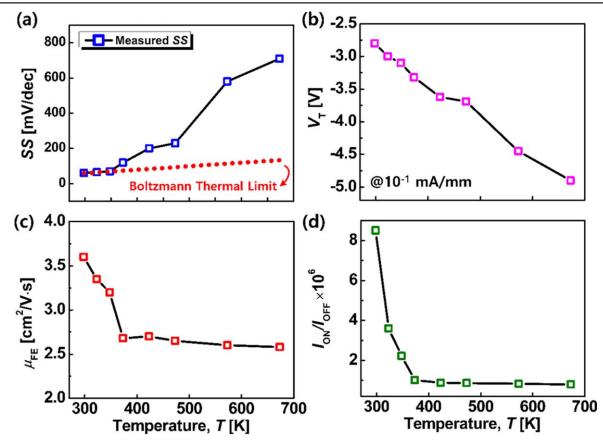

gradually increase as the temperature increases, our proposed tri-gate  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FETs have more stable characteristics for temperatures up to 400 °C compared to previous results [6, 13]. The variations in the extracted SS,  $V_{\rm T}$ , field-effect mobility  $(\mu_{\rm FE})$ , and  $I_{\rm ON}/I_{\rm OFF}$ , as a function of temperature are plotted in figure 4. The value of SS increases from 61 mV dec<sup>-1</sup> to 710 mV dec<sup>-1</sup> and V<sub>T</sub> shifts toward a negative direction due to thermally excited carriers from interface states between the channel and the gate dielectric, as shown in figures 4(a) and (b). The interface trap density  $(D_{it} [eV^{-1} cm^{-2}])$  of the fabricated devices is extracted to  $1.0 \times 10^{11} \text{ eV}^{-1} \text{ cm}^{-2}$  at RT. The significant increase of SS beyond Boltzmann thermal limit indicates a large amount  $D_{\rm it}$  of 1.6  $\times$  10<sup>13</sup> eV<sup>-1</sup> cm<sup>-2</sup> could be activated at 400 °C. In addition,  $\mu_{\rm FE}$  decreases also due to the increased D<sub>it</sub> at the interface and the phonon scattering in channel at high temperatures as shown in figure 4(c) [6, 13, 27]. We should also note that, even at 400 °C,  $I_{ON}/I_{OFF}$ was observed to be approximately  $3 \times 10^5$ , as shown in figure 4(d). The tri-gate  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FETs with ALD Al<sub>2</sub>O<sub>3</sub> as gate dielectric demonstrate robust electrical performances at high temperatures. Furthermore, the measured I-V characteristics at RT were again obtained after cooling the device from high temperature to RT.

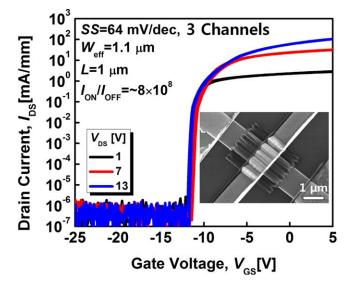

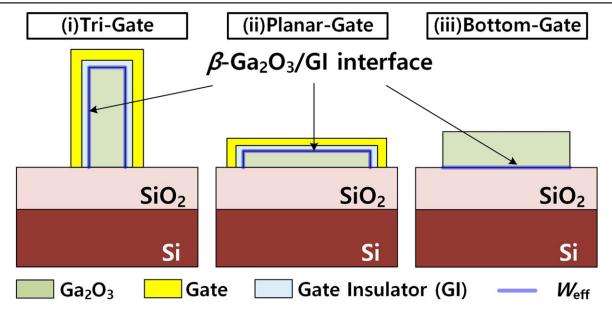

As shown in figure 5, we also demonstrated the feasibility of the multi-channel tri-gate  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FETs for a high integration density. The inset shows the SEM image for top view of the fabricated device with 3 channels. In case of multi-channel devices, overall device performances are also comparable to the single-channel devices. To provide clear evidences for advantages of tri-gate  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FETs, we fabricated three types of devices with different gate structures ((i) tri-gate, (ii) planar-gate, and (iii) bottom-gate) under same process conditions and investigated the impact of the tri-gate  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FETs via comparison with other devices, as shown in figure 6. Table 1 shows the comparison data of the fabricated devices with different gate structures. It is noteworthy

**Figure 4.** Temperature dependences (RT-400 °C) at  $V_{\text{DS}} = 1$  V of typical device parameters such as (a) SS (dashed line: Boltzmann thermal limit of SS), (b)  $V_{\text{T}}$ , (c)  $\mu_{\text{FE}}$ , and (d)  $I_{\text{ON}}/I_{\text{OFF}}$  of the tri-gate  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FETs on the SiO<sub>2</sub>/Si substrate.

**Figure 5.** Measured  $I_{\text{DS}}-V_{\text{GS}}$  characteristics of the fabricated  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FETs with multi channels. Inset shows SEM image for top view of the fabricated device with 3 channels.

that the tri-gate  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FETs have high channel ratio  $(W_{\text{eff}}/\text{perimeter} \text{ of channel width } (W_{\text{peri}}))$  of 0.85 and aspect ratio (AR) of 2 resulting in better electrical performances such as  $I_{\text{ON}}/I_{\text{OFF}}$ , SS, and  $D_{\text{it}}$  [28, 29]. In this regard, minimizing the device degradation caused by interface states and

modulating the effective charges from  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> channel in trigate  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FETs can be important since the switching characteristics are very strongly influenced by interface between  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> and bottom SiO<sub>2</sub> substrate.

A benchmark of the fabricated tri-gate  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FETs is summarized in table 2. The overall electrical performances of the fabricated tri-gate  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FETs with a single channel are improved over different types of devices reported previously. In particular, our proposed device is highly scalable with an active channel area of 0.05  $\mu$ m<sup>2</sup> by employing an extremely scaled  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> structure. The  $D_{it}$  of the fabricated device shows a high-quality interface compared with previously reported results [30, 31]. In the positive bias stress experiments, we also found accumulation of positive charges at the bottom-interface (or edges) leads to the degradation of *SS* and negative shift of  $V_T$  [32]. Therefore, more comprehensive study is required for the investigation of stress-induced instability considering the device geometry, as a further study.

#### 4. Conclusion

In this study, top-gate tri-gate nano-membrane  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FETs were successfully demonstrated for the first time. By adopting the single fin-like structure with a  $W_{ch}$  of 50 nm, the fabricated devices have improved subthreshold slope and  $I_{ON}/I_{OFF}$

Figure 6. Schematics of cross-sectional view for the fabricated devices with different gate structures: (i) tri-gate, (ii) planar-gate, (iii) bottom-gate.

| $@V_{\rm DS} = 1 \text{ V}$               | Sample #1                      | Sample #2               | Sample #3                |  |

|-------------------------------------------|--------------------------------|-------------------------|--------------------------|--|

| Structure                                 | Single channel                 | Planar                  | Bottom-Gate              |  |

| Gate dielectric                           | Al <sub>2</sub> O <sub>3</sub> | $Al_2O_3$               | SiO <sub>2</sub>         |  |

| $I_{\rm ON}/I_{\rm OFF}$                  | $\sim 1.3 \times 10^7$         | $\sim 9.5 \times 10^6$  | $\sim 1.2 \times 10^{6}$ |  |

| $SS_{min}$ [mV dec <sup>-1</sup> ]        | 61                             | 100                     | 250                      |  |

| Туре                                      | Flake                          | Flake                   | Flake                    |  |

| $D_{\rm it} [{\rm eV}^{-1}{\rm cm}^{-2}]$ | $\sim 1 	imes 10^{11}$         | $\sim 9 \times 10^{11}$ | ${\sim}1	imes10^{12}$    |  |

| W <sub>eff</sub>                          | 250 nm                         | $1 \ \mu m$             | 1.5 μm                   |  |

| Channel ratio                             |                                |                         |                          |  |

| $(W_{\rm eff}/W_{\rm peri})$              | 0.85                           | 0.55                    | 0.45                     |  |

| Aspect ratio (AR)                         | 2                              | 0.12                    | 0.1                      |  |

Table 1. Comparison data with different gate structures.

Table 2. Benchmarking for electrical performances of  $Ga_2O_3$  FETs.

|                                                          | This work                | Reference [13]         | Reference [14]           | Reference [15]         |

|----------------------------------------------------------|--------------------------|------------------------|--------------------------|------------------------|

| $I_{\rm ON}/I_{\rm OFF}$ (Max.)                          | ${\sim}1.5 \times 10^9$  | $\sim 7 \times 10^7$   | $\sim 5 \times 10^5$     | $\sim 1 \times 10^9$   |

| $SS_{min}$ [mV dec <sup>-1</sup> ]                       | 61                       | 70                     | 158                      | 200                    |

| # of Ch.                                                 | Single                   | —                      | 48                       | 20                     |

| Туре                                                     | Flake                    | Flake                  | MOVPE                    | Epitaxial growth       |

| $D_{\rm it}$ (Max.) [eV <sup>-1</sup> cm <sup>-2</sup> ] | ${\sim}1 \times 10^{11}$ | —                      | ${\sim}1 \times 10^{12}$ | _                      |

| Temp.                                                    | $RT\sim 400~^\circ C$    | $RT\sim 250~^\circ C$  | RT                       | RT                     |

| $V_{\rm hys}$                                            | 30 mV                    | 30 mV                  | 700 mV                   | 100 mV                 |

| I <sub>DS_max</sub>                                      | $350 \text{ mA mm}^{-1}$ | $1 \text{ mA mm}^{-1}$ | $3 \text{ mA mm}^{-1}$   | $1 \text{ kA cm}^{-2}$ |

| W <sub>eff</sub>                                         | 250 nm                   | $7 \ \mu m$            | $24 \ \mu m$             | 50 µm                  |

resulting from enhanced top gate controllability. Moreover, the fabricated devices demonstrate sustainable reliability under high temperatures of up to 400 °C, validating its use in applications involving harsh environments. Multi-channel

devices also represent improved electrical performances comparable to single-channel devices for high integration density. Consequently, we expect that tri-gate  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> FETs have the potential as a low-cost and high-performance power device technology after the establishment of epitaxy materials.

#### Acknowledgments

This work was supported in part by the Office of Naval Research's Naval Enterprise Partnership Teaming with Universities for National Excellence under Grant N00014-15-1-2833 and in part by Applications and Systems-Driven Center for Energy-Efficient Integrated NanoTechnologies (ASCENT), one of six centers in Joint University Microelectronics Program (JUMP), as Semiconductor Research Corporation (SRC) Program sponsored by Defense Advanced Research Projects Agency (DARPA). The work of Tae Joon Park and Shriram Ramanathan was supported by Energy Frontier Research Centers (EFRC) funded by the U.S. Department of Energy (DOE), Office of Science, Basic Energy Sciences (BES), under Award DE-SC0019273.

#### Data availability statement

All data that support the findings of this study are included within the article (and any supplementary files).

#### **ORCID** iDs

Hagyoul Bae https://orcid.org/0000-0002-2462-4198

#### References

- [1] Higashiwaki M and Jessen G H 2018 Appl. Phys. Lett. 112 060401

- [2] Li W, Nomoto K, Hu Z, Nakamura T, Jena D and Xing H G 2019 IEDM Tech. Dig. 270

- [3] Xu W et al 2019 IEDM Tech. Dig. 274

- [4] Tsao J Y et al 2018 Adv. Electron. Mater. 4 1600501

- [5] Higashiwaki M, Sasaki K, Wong M H, Kamimura T, Krishnamurthy D, Kuramata A, Masui T and Yamakoshi S 2013 IEDM Tech. Dig. 707

- [6] Higashiwaki M, Sasaki K, Murakami H, Kumagai Y, Koukitu A, Kuramata A, Masui T and Yamakoshi S 2016 Semicond. Sci. Technol. 31 034001

- [7] Pearton S J, Yang J, Cary P H, Ren F, Kim J, Tadjer M J and Mastro M A 2018 Appl. Phys. Rev. 5 011301

- [8] Si M, Yang L, Zhou H and Ye P D 2017 ACS Omega 2 7136

- [9] Kim M, Seo J H, Singisetti U and Ma Z 2017 J. Mater. Chem. C 5 8338

- [10] Kim M, Seo J H, Zhao D, Liu S C, Kim K, Lim K, Zhou W, Waks E and Ma Z 2016 J. Mater. Chem. C 5 264

- [11] Casady J B and Johnson R W 1996 Solid-State Electon.

39 1409

- [12] Neudeck P G, Okojie R S and Chen L Y 2002 Proc. IEEE 90 1065

- [13] Ma J and Yoo G 2019 IEEE Electron Device Lett. 40 1317

- [14] Chabak K D et al 2016 Appl. Phys. Lett. 109 213501

- [15] Hu Z, Nomoto K, Li W, Tanen N, Sasaki K, Kuramata A, Nakamura T, Jena D and Xing H G 2018 *IEEE Electron Device Lett.* 39 869

- [16] Zhou H, Si M, Alghamdi S, Qiu G, Yang L and Ye P D 2017 IEEE Electron Device Lett. 38 103

- [17] Chabak K D et al 2018 IEEE Electron Device Lett. 39 67

- [18] Dong H et al 2019 IEEE Electron Device Lett. 40 1385

- [19] Choi Y K, Lindert N, Xuan P, Tang S, Ha D, Anderson W, King T J, Bokor J and Hu C 2001 *IEDM Tech. Dig.* 421

- [20] Kim S M et al 2004 IEDM Tech. Dig. 639

- [21] Zhang L, Verma A, Xing H and Jena D 2017 Japan. J. Appl. Phys. 56 030304

- [22] Ye P D et al 2003 Appl. Phys. Lett. 83 180

- [23] Hinkle C L et al 2008 Appl. Phys. Lett. 92 071901

- [24] Noh J, Alajilouni S, Tadjer M J, Culbertson J C, Bae H, Si M, Zhou H, Bermel R A, Shakouri A and Ye P D 2019 *IEEE J*. *Electron Devices Soc.* 7 914

- [25] Bae H, Kim S, Bae M, Shin J S, Kong D, Jung H, Jang J, Lee J, Kim D H and Kim D M 2011 IEEE Electron Device Lett. 32 761

- [26] Sasaki K, Higashiwaki M, Kuramata A, Masui T and Yamakoshi S 2013 Appl. Phys. Express 6 086502

- [27] Zhang Y et al 2018 Appl. Phys. Lett. **112** 173502

- [28] Cheng H W and Li Y 2009 Semicond. Sci. Technol. 24 115021

- [29] Park S H, Liu Y, Kharche N, Jelodar M S, Klimeck G, Lundstrom M S and Luisier M 2012 *IEEE Trans. Electron Devices* 59 2107

- [30] Zhou H, Alghamdi S, Si M, Qiu G and Ye P D 2016 IEEE Electron Device Lett. 37 1411

- [31] Zeng K, Jia Y and Singisetti U 2016 *IEEE Electron Device Lett.* **37** 906

- [32] Mativenga M, Seok M and Jang J 2011 Appl. Phys. Lett. 99 122107